# Details of the First 3D-IC Multi-Project Wafer Run

#### **>> OUTLINE:**

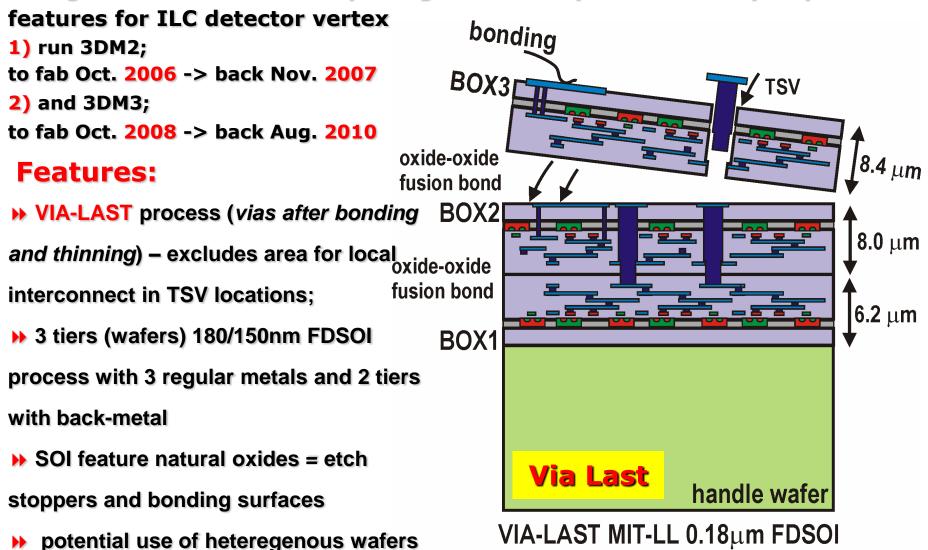

- 1) involvement in 3D projects at Fermilab

- 2) 3D-IC consortium run

- 3) verification including 3D LVS

- 4) next steps

- 5) summary but no conclusions

# G. Deptuch, M.Demarteau, J.Hoff, R. Lipton, R. Patti<sup>1</sup>, A. Shenai, M. Trimpl, R.Yarema, T.Zimmerman

<sup>1</sup> Tezzaron Semiconductor

#### **Involvement in 3D projects at Fermilab**

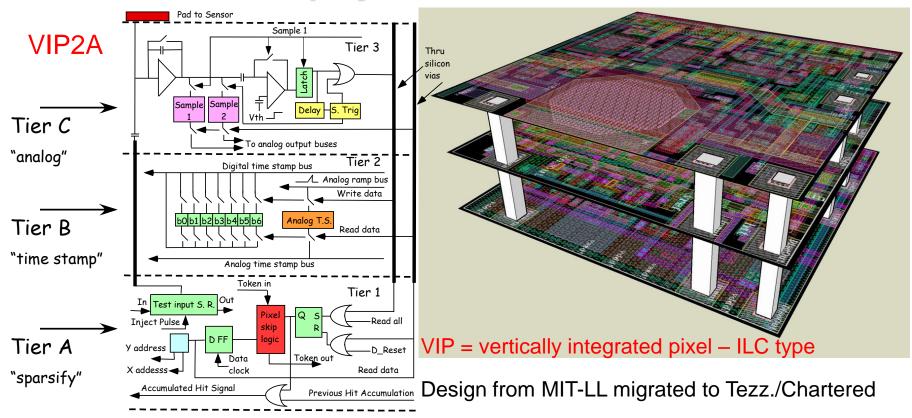

Two generations of Vertically Integrated Pixel (VIP1 & VIP2A) chips with

#### **Involvement in 3D projects at Fermilab**

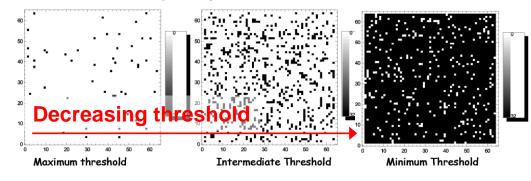

Data readout out using data sparsification scheme.

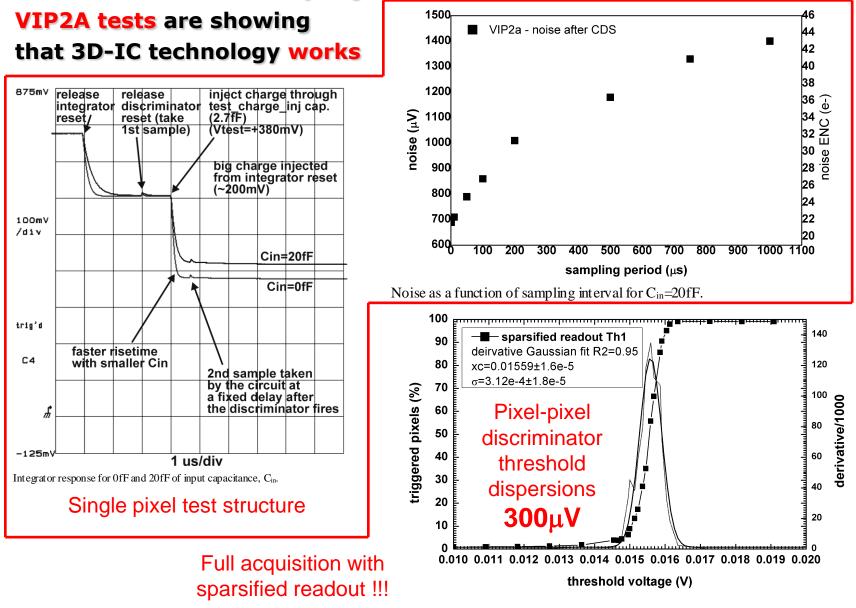

VIP1 found to be functional. Architecture proven but: VIP1 yield was low. VIP2A s submitted including adaptations to analog design in FDSOI and played safe face to laboratory scale process Focus has shifted from working in FD SOI to bulk CMOS processes

### Involvement in 3D projects at Fermilab

**‡** Fermilab

## **3D-IC consortium run**

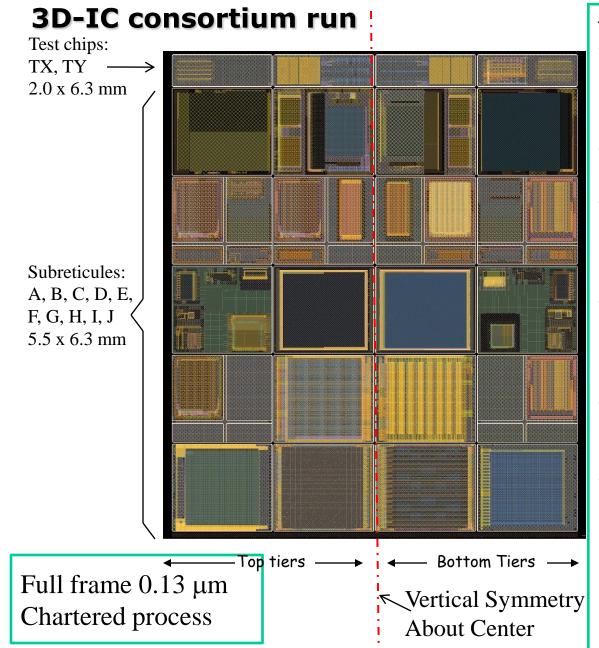

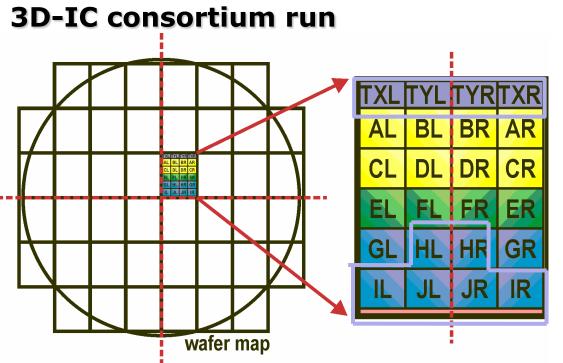

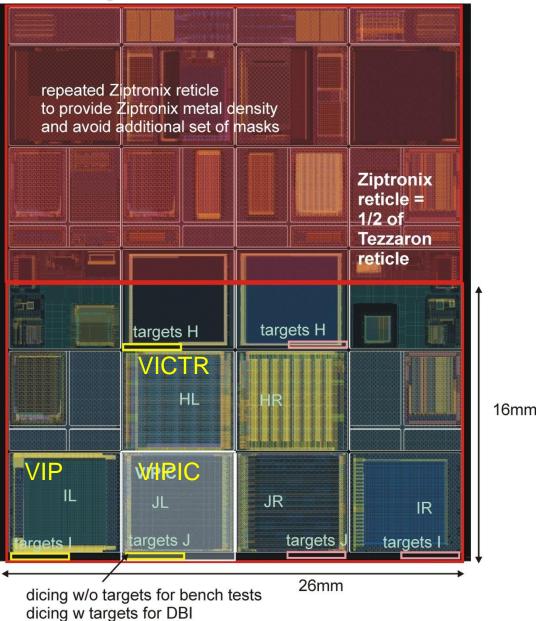

Migrated VIP2A->VIP2B design + 2 other designs from Fermilab and 9 other subreticules from 3D-IC consortium institutions submitted on a Fermi MPW

#### 1) to fab May/June 2009 -> back not yet

#### **Features:**

▶ 8" wafers, large ~26×31 mm<sup>2</sup> reticule,

1P/6M (8M) + RDL, DNW, SM MIM Caps, LP

(chosen), standard VT + low VT, + Zero Vt +

IO MOSFETs, HR poly resistors,

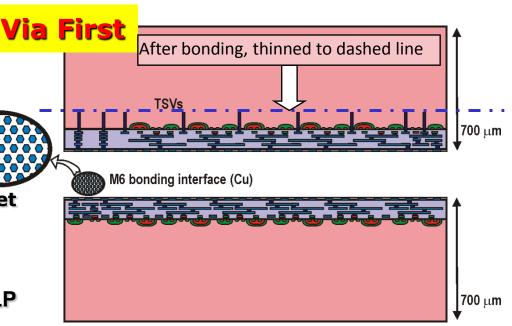

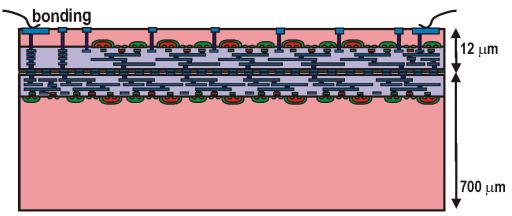

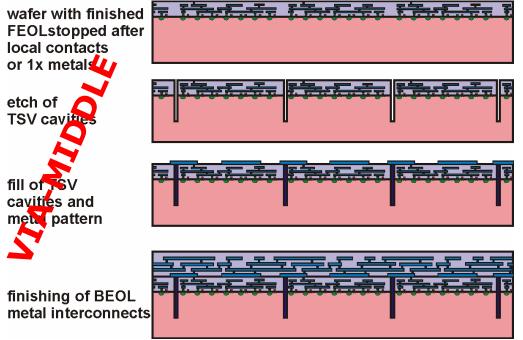

embedded TSVs

Tungsten TSVs are part of the FEOL, φ=1.3 μm, 3.8 μm rec. spacing and 6 μm depth,

▶ 6<sup>th</sup> metal used as a bond interface for face-face Cu-Cu thermo-compression bonding

**‡** Fermilab

0.13  $\mu$ m bulk CMOS by Chartered with Tezzaron 3D via-first technology

#### **3D-IC consortium run**

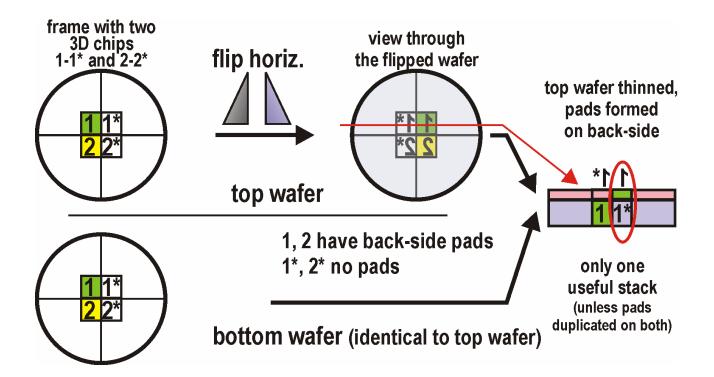

#### Economical solution employed on the 3D-IC run

Alternative would be to fabricate two sets of wafers from two sets of masks if there were enough customers

#### - Run organization:

- Consortium established by Fermilab in late 2008, now 17 members; 6 countries (USA, Italy, France, Germany, Poland, Canada)

- first designers' meeting: Dec. 2008, then Feb., Mar., and May 2009

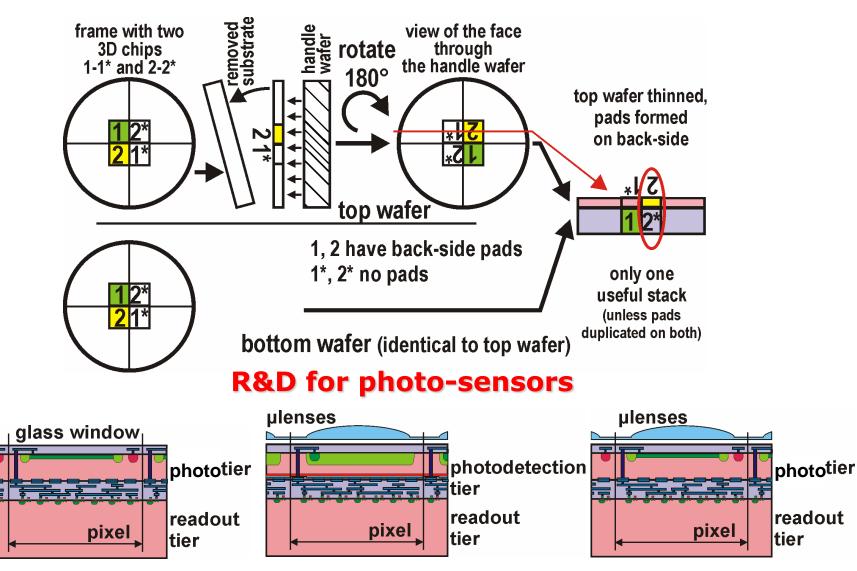

- Initial designs for MPW run completed in May 2009; 2 tier 3D chip, single mask set face-to-face bonding; Chartered 130 nm CMOS

- Numerous problems were encountered with designs, software tools at Tezzaron, shifting Chartered requirements, etc.

- MPW frame accepted by Chartered in March 2010, Waiting for chips – Oct./Nov. 2010

- Delay appears related to Global/Chartered decision to move some equipment from prototype line, where 3D wafers are done, to the production line due to increase production demands

# **‡** Fermilab

Division of the frame into 12 subreticule pairs: left-right. – Fermilab designs:

- H = VICTR; short pixel realizing p<sub>t</sub> cut for L1 trigger embedded in tracker for CMS @ SLHC

- I = VIP2b; time stamping pixel for vertex detector @ ILC

- J = VIPIC; very high frame rate with sparsification pixel for Xray Photon Correlation Spectroscopy @ light source

- TX, TY test structures (single transistors and subcircuits)

- Depth of 3D-IC exploration:

- ideas for bonding fabricated chips to detectors were present from the beginning of chip design

- complexity of envisaged solutions was growing – from simple bonding apetite has grown to full double side connectivity

- Physical and functional verification

- continuous checking of designs by Fermilab and Tezzaron → identified numerous problems:

- + layer map tables, bond interfaces, mirroring of designs in frame,

- + different DRC violations found with Assura, Calibre, and Magma + problems with CAD software

- MicroMagic, Calibre and Magma

- + newer DRC versions uploaded

- Fabrication schedule

- order is for 31 wafers for all users

- 8 weeks for wafer fabrication.

- 4 weeks for 3D assembly

- 5 wafers for DBI try-out from Fermilab

# **‡** Fermilab

## **Verification including 3D LVS**

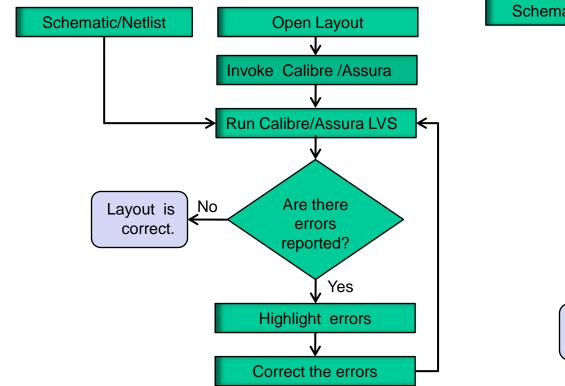

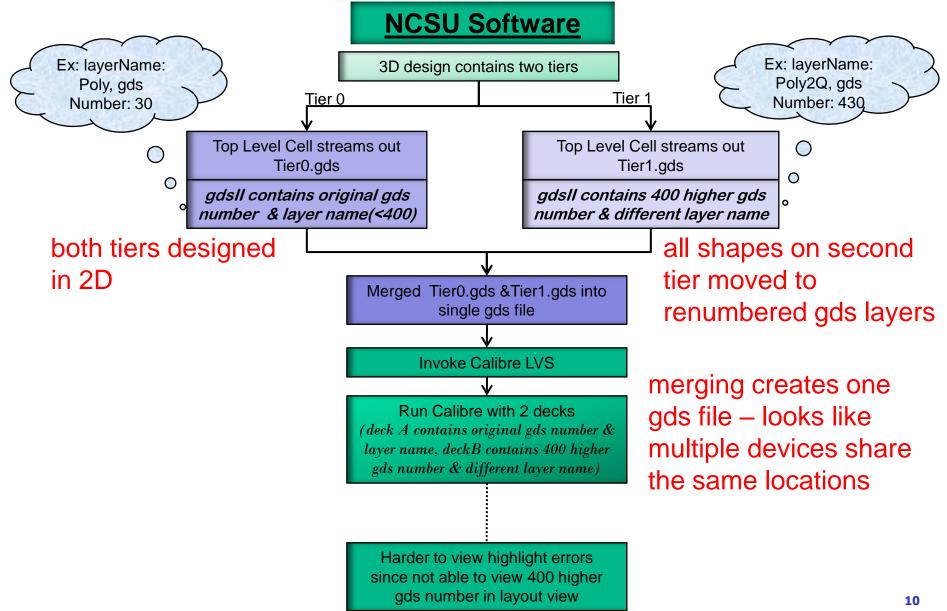

Fig. I: Basic LVS Flow Using Calibre or Assura

flow for 2D-IC

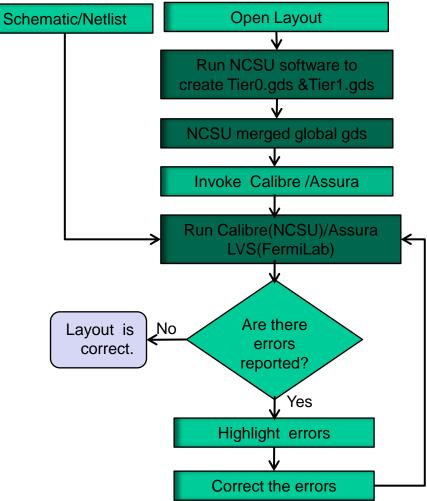

Fig. 2: 3D LVS Flow Using Calibre or Assura

flow for 3D-IC

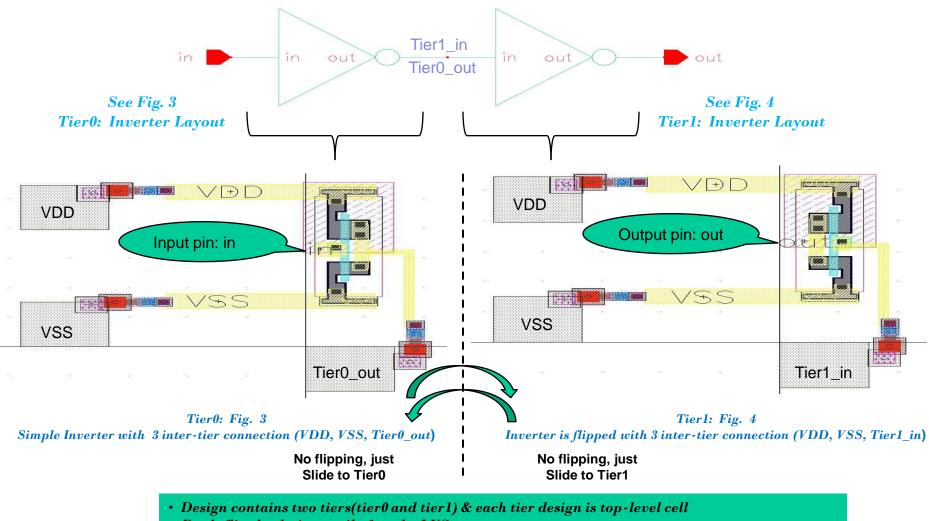

### **Verification including 3D LVS**

### **Verification including 3D LVS**

- Don't flip the design until after the LVS

- Connectivity are done between two tiers through Metal 6

- Sliding either direction tier0 or tier1 will connect both tiers VDD, VSS, and Tier0\_out to Tier1\_in

- Available pins after sliding: VDD, VSS, in, & out

## Next steps

# **‡** Fermilab

#### **Next steps**

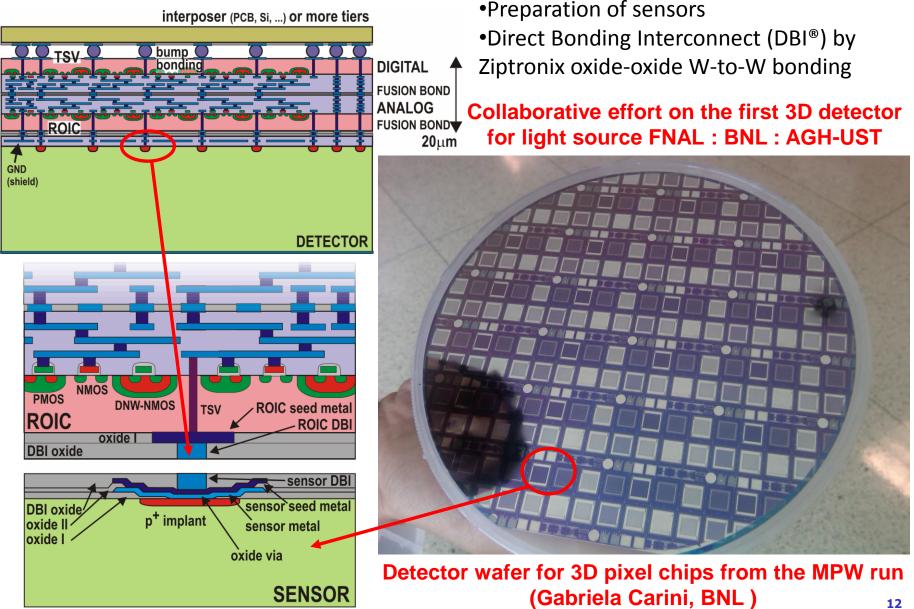

#### Readiness for DBI bonding

- DBI bonding will be done at Ziptronix

- Chips: H (VIP), I (VICTR), J (VIPIC) designed for DBI bonding

- Alignment targets required for aligning:

a) deposition of seed and DBI post metal requires stepper alignment targets

b) DBI bonding requires bond alignment targets

- Targets placed in two locations:

a) stepper alignment targets in the first vertical internal dicing street

b) DBI bonding targets in the dicing streets above the chip H and below chips I and J

- Stepper alignement targets include use of M1 on the frame

- Bonding alignment targets require UR transparency on the frame

- Targets use Ziptronix layers to be deposited on the frame and sensors

- Singulation of chips

- Fermilab will dice one 3D wafer for to provide chips for bench testing (no detectors) size 5.5×6.3 mm<sup>2</sup>

- Fermilab will deliver 5 wafers for singulation and DBI bonding to the BNL sensors (5.6×6.3 mm<sup>2</sup>)

### Next steps

- 2 tier face to face bonded wafer

- 130 nm CMOS for both tiers

Fermilab, has worked closely with MOSIS/CMP and CMC to establish MPW runs for 3D circuits with commercial silicon brokers. Next submission of 3D chips planned for Spring 2011 via CMP/CMC/MOSIS partnership

#### Developments for Future Runs

- Chartered to stop TSVs on 8 inch 0.13 CMOS wafers for the foreseeable future

- Chartered agrees to process wafers from FEOL through M4

- Tezzaron will have SVTC add TSVs from M4 down into the substrate and complete the BEOL processing including the bond interface metalization

- Implication is that space will need to be left open on M1-M4 for the vias to pass through.

- Future potential benefit will be that wafers from other foundries can use the Tezzaron 3D process.

ANNOUNCEMENT

#### CMP/CMC/MOSIS partner to introduce a 3D-IC process

Grenoble, France, 22 June 2010, CMP/CMC/MOSIS are partnering to offer a 3D-IC MPW service based on Tezzaron's SuperContact technology and GLOBALFOUNDRIES 130nm CMOS.

#### Next steps (separate effort)

Front-side illumination+shallow junctions = good short wavelength response

#### Summary

#### Attempts made to explore the 3D technology has shown:

Successful Implementation of circuits that go beyond the complexity of the test structures and targeting real applications, are achievable

There is no universal manufacturing technology of integrated circuits 3D – such a situation is expected to maintain in the near future

The processing for 3D is new for the industry (TSV cut, alignment, etc.); many surprises are lurking on the users as the industry sticks to strict rules and these rules are not yet settled for 3D techniques, time needed for processing far exceeds initial estimations

It is not unreasonable to expect that with the popularization of 3D techniques, which undoubtedly will happen in the near future, many of the problems find their solution

The first run has currently its wafers the technology will be facilitated being refabricated due to misalignment of reticles (targeting maximum # of chips / wafer) preventing w-to-w bonding – priority at the fab;

Commercial brokers MOSIS / CMP / CMC have recognized opportunities and decided to announce 3D MPW service based on experience Fermilab - the access to the technology will be facilitated